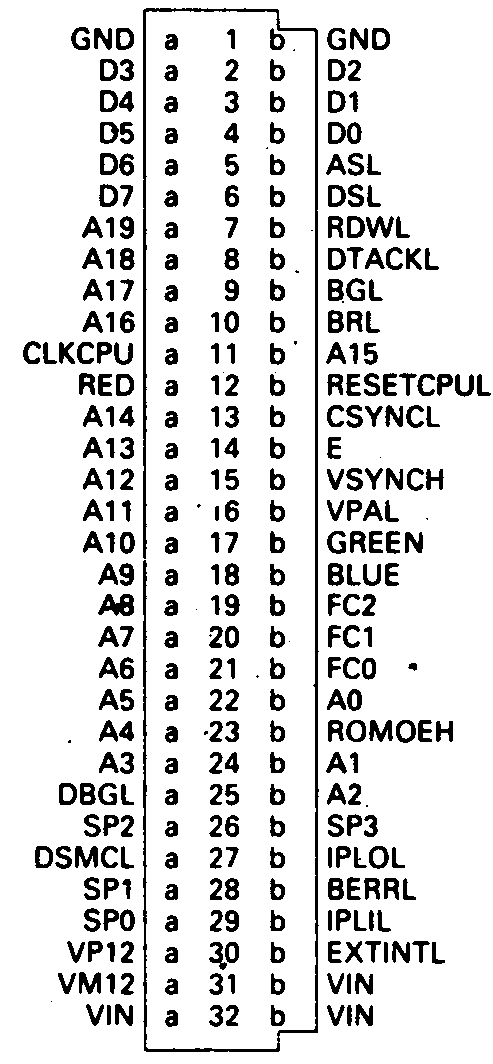

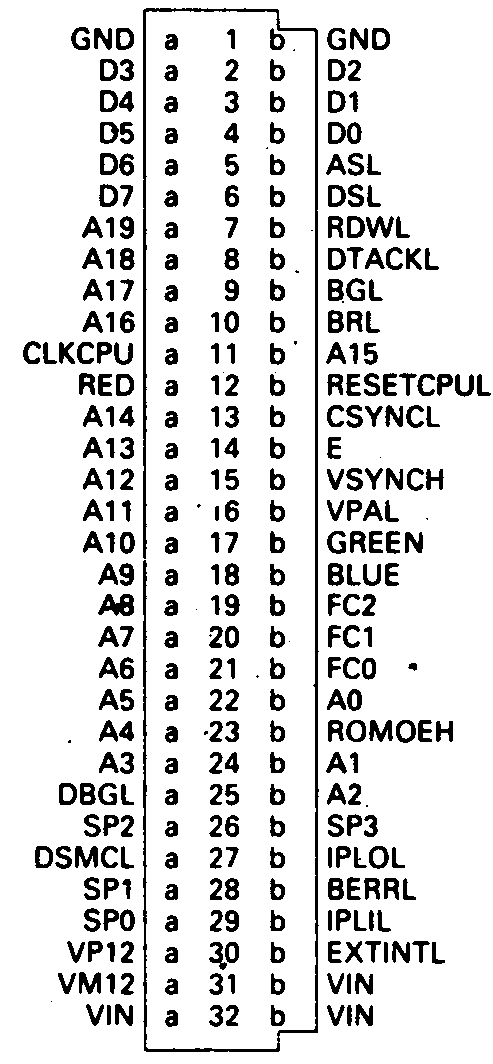

Figura F.1 - Señales disponibles en el conector lateral

| QL Programación Avanzada | ||

|---|---|---|

| Anterior | Siguiente | |

Este apéndice explica la filosofía básica de la expansión 'hardware' del QL. Esta información se puede ampliar con un buen libro sobre interconexiones con el microprocesador 68008. Los detalles sobre la expansión de la ROM se incluyen en el apéndice C.

El QL ha sido diseñado con la facilidad de añadir una cantidad considerable de 'hardware'. Éste se puede conectar al QL por medio del conector de expansión que hay en el lateral izquierdo. El acceso está tapado normalmente por una pieza de plástico negro. Si se quita esta tapa, es posible ver un conector DIN-41612 macho de 64 vías. La figura F.1 nos muestra un esquema del mismo.

Figura F.1 - Señales disponibles en el conector lateral

Las señales que aparecen seguidas de una L están activas cuando están bajas.

Para conocer la descripción de cada una de estas señales y su forma de operación, se debe consultar un libro de 68008.

Todas las señales del 68008 salen por el conector de expansión, por lo que es posible conectar cualquier tipo de periférico para el QL. Estos periféricos se colocarán en tarjetas enchufables. Solamente se puede añadir una de estas tarjetas al QL estándar. Para permitir una mayor flexibilidad, se dispondrá pronto de un módulo de expansión que proporcione varias ranuras para poder conectar distintos tipos de periféricos a medida que estén disponibles.

| A0 a A19 | Líneas de dirección del 68008 |

| ASL | Dirección de 'strobe' (indica direcciones válidas) |

| RDWL | Lectura/Escritura |

| DSL | 'Strobe' de los datos |

| BGL | Permiso para las líneas de transmisión |

| DSMCL | 'Strobe' de datos Sostenido (chip maestro) |

| CLCKCPU | Reloj de la CPU |

| E | Señal de habilitación de periféricos 6800 |

| RED | Salida vídeo rojo |

| BLUE | Salida vídeo azul |

| GREEN | Salida vídeo verde |

| CSYNCL | Señal de sincronismo del vídeo compuesto |

| VSYNCH | Señal de sincronismo vertical |

| ROMOEH | Salida de ROM habilitada |

| FC0 | Estado del procesador |

| FC1 | Estado del procesador |

| FC2 | Estado del procesador |

| RESETCPUL | Iniciación de la CPU |

| D0 a D7 | Líneas de transmisión de datos |

| DTACKL | Árbitro de líneas de transmisión |

| BRL | Petición a las líneas de transmisión |

| VPAL | Dirección periférica válida |

| IPL0L | Prioridad de interrupción de nivel 0 |

| IPL1L | Prioridad de interrupción de nivel 1 |

| BERRL | Error de líneas de transmisión |

| EXTINTL | Interrupción externa |

| DBGL | Recogida de datos de las líneas de transmisión |

| SP0 a SP3 | Líneas de selección de periféricos (hasta 16) |

| VIN | 9V DC nominales (7V mínimo) a 500mA máximo |

| VM12 | −12V |

| VP12 | +12V |

| GND | 0V (tierra de señales y alimentación) |

Hay dos tipos de tarjetas de expansión, de memoria y de periféricos.

El mapa de memoria entre las direcciones $40000 y $BFFFF ha sido asignado como memoria adicional (por lo tanto se puede añadir hasta medio 'megabyte' (512K octetos)). Esta memoria es contigua desde $40000 hacia arriba. Solamente se puede conectar a un tiempo una de estas tarjetas de memoria adicional. Cuando se enciende el QL, el QDOS comprueba si está disponible esta memoria.

Las tarjetas periféricas son muy interesantes. Cada una puede contener una ROM con controladores (ver sección 9) para los diferentes dispositivos que contiene la tarjeta. Todos los controladores tienen posiciones independientes, debido a la forma en que se asignan las posiciones de memoria a las diferentes tarjetas.

El conector del QL tiene cuatro líneas de seńal: SP0, SP1, SP2 y SP3. Todas ellas tienen su masa conectada a la tarjeta principal. Cada tarjeta de expansión contiene un circuito que produce un número diferente. Los circuitos de cada tarjeta deben comparar la dirección en SP0-SP3 con la que hay en las líneas A14-A17. Si son iguales, y está seleccionada el área de memoria de la tarjeta, la tarjeta es seleccionada. Cada tarjeta ocupa un hueco de 16K octetos en la memoria comprendida entre las direcciones $C000+$4000*n, donde n es el número introducido en cada tarjeta particular. De esta forma se puede comprender por qué cada tarjeta tiene su posición independiente. Cuando se conectan varias tarjetas, se pueden colocar en cualquier lugar de la parte superior de la memoria.

El 68008 no tiene un control completo de todas las líneas de transmisión. Cuando se transfiere información desde la memoria al circuito de vídeo, el ULA del retiene las líneas usando la señal DTACKL. El acceso a memoria se controla solamente con DSL, y no se usa ASL.

El reparto del mapa de memoria se realiza por los estados lógicos de las líneas altas de dirección. Para ayudarle a comprender la decodificación necesaria, vea la tabla que le damos a continuación:

| A19 | A18 | A17 | A16 | A15 | A14 | Rango direc. | |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | X | 00000-07FFF | ROM sistema (32K prim.) |

| 0 | 0 | 0 | 0 | 1 | 0 | 08000-9BFFF | ROM sistema (16K exp.) |

| 0 | 0 | 0 | 0 | 1 | 1 | 0C000-0FFFF | ROM enchuf. hasta 16K |

| 0 | 0 | 0 | 1 | 0 | X | 10000-17FFF | Reservadas |

| 0 | 0 | 0 | 1 | 1 | 0 | 18000-1BFFF | Registro internos y ES |

| 0 | 0 | 0 | 1 | 1 | 1 | 1C000-1FFFF | 128K RAM estándar |

| 0 | 0 | 1 | X | X | X | 20000-3FFFF | Reservadas |

| 0 | 1 | X | X | X | X | 40000-7FFFF | 256K RAM de expansión |

| 1 | 0 | X | X | X | X | 80000-BFFFF | 256K RAM de expansión |

| 1 | 1 | X | X | X | X | C0000-FFFFF | Expansión 'hardware' |

En un QL no expandido las líneas A18 y A19 no se usan nunca. Cuando se añaden periféricos, deben inhabilitar los circuitos principales del QL mientras reconoce las direcciones válidas. Esto se realiza poniendo alta la señal DSMCL. Se recomienda que se use para esto un transistor NPN de conmutación rápida.

A todas las señales de las líneas se pueden conectar dos TTL de baja potencia como máximo. El periférico debe suministrar las señales DTACKL (reconocimiento de transferencia de datos) o VPAL (dirección periférica válida) según se requiera, y debe inhabilitar DSMCL ('strobe' de datos del chip maestro).

El módulo de expansión debe proporcionar memoria intermedia extra de líneas. La memoria intermedia de datos se habilita cuando A18 y A19 están a 1, o si DGBL (señal de recogida de datos) es puesta a 1 por cualquier tarjeta periférica. Si se usa DBGL, se debe reforzar por un circuito de colector abierto. Cuando se conecta el módulo de expansión, se pone a cero RESETCPUL mientras se enciende el módulo de expansión. Si se apaga el módulo de expansión, RESETCPUL se pone a 0.

| Anterior | Tabla de contenidos | Siguiente |

| Descripción de la pantalla | Códigos de error |